Our Products

Comprehensive industrial automation solutions for global industries

Contact us

If you are interested in our products and want to know more details,please Contact us,we will reply you as soon as we can.

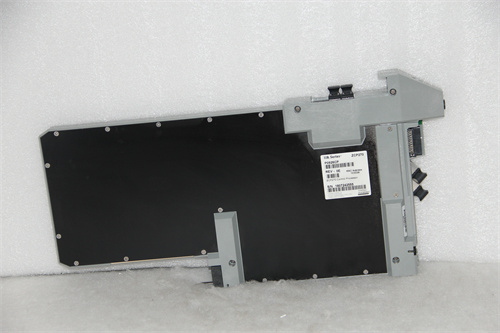

Foxboro FBM232 P0926GW Sensor Low Frequency Measurement

Manufacturer: Foxboro (Schneider Electric)

Product Number: FBM232 (P0926GW)

Category: Sensor Input Module / Low Frequency Measurement Module

System Platform: Foxboro I/A Series Distributed Control System (DCS)

Function: Acquires low-frequency sensor signals for vibration monitoring and process measurement

Application: Low-frequency vibration monitoring, process measurement, rotating machinery monitoring, condition monitoring

Product Description

FBM232 P0926GW is different from general ADCs, ∑-Δ ADCs are not quantized directly according to the size of the first sample, but according to the difference between the previous value and the last value, the so-called increment size. In a sense, it is quantized and encoded according to the envelope of the signal waveform. The σ-δ ADC consists of two parts, the first part is an analog σ-δ modulator, and the second part is a digital extraction filter, as shown in Figure 5. The σ-δ modulator samples the input analog signal at a very high sampling frequency, and quantifies the difference between the two samples at a low level, so that the digital signal expressed by a low level digit is ∑-Δ code. Then the ∑-Δ code is sent to the second part of the digital extraction filter for extraction and filtering, so as to obtain high resolution linear pulse code modulation digital signal. Therefore, the decimation filter is actually equivalent to a code converter. Because ∑–△ has an extremely high sampling rate, often many times higher than the Nyquist sampling frequency, the ∑–△ converter is also called an over-sampled A/D converter.

Currently, FBM232 P0926GW ADCs are divided into four categories:

(1) High-speed ADC;

(2) Modem ADC;

(3) encoder ADC;

(4) Sensor low-frequency measurement ADC.

Foxboro FBM232 P0926GW Sensor Low Frequency Measurement

Manufacturer: Foxboro (Schneider Electric)

Product Number: FBM232 (P0926GW)

Category: Sensor Input Module / Low Frequency Measurement Module

System Platform: Foxboro I/A Series Distributed Control System (DCS)

Function: Acquires low-frequency sensor signals for vibration monitoring and process measurement

Application: Low-frequency vibration monitoring, process measurement, rotating machinery monitoring, condition monitoring

Product Description

FBM232 P0926GW is different from general ADCs, ∑-Δ ADCs are not quantized directly according to the size of the first sample, but according to the difference between the previous value and the last value, the so-called increment size. In a sense, it is quantized and encoded according to the envelope of the signal waveform. The σ-δ ADC consists of two parts, the first part is an analog σ-δ modulator, and the second part is a digital extraction filter, as shown in Figure 5. The σ-δ modulator samples the input analog signal at a very high sampling frequency, and quantifies the difference between the two samples at a low level, so that the digital signal expressed by a low level digit is ∑-Δ code. Then the ∑-Δ code is sent to the second part of the digital extraction filter for extraction and filtering, so as to obtain high resolution linear pulse code modulation digital signal. Therefore, the decimation filter is actually equivalent to a code converter. Because ∑–△ has an extremely high sampling rate, often many times higher than the Nyquist sampling frequency, the ∑–△ converter is also called an over-sampled A/D converter.

Currently, FBM232 P0926GW ADCs are divided into four categories:

(1) High-speed ADC;

(2) Modem ADC;

(3) encoder ADC;

(4) Sensor low-frequency measurement ADC.

Need a Custom Automation Solution?

Our team of experts can design and implement a tailored automation system to meet your specific requirements.

Loading comments...

Loading comments...